D-Latches not that often

used in digital designs - but they very important in concern

with PLC programming.

|

|

|

|

|

|

|

|

|

|

|

Basic implementation of a

D-Latch with NAND-gates.

Read more in

Wakerly 4ed - 7.2.4

Or read more in

Mark - 6.1.2

|

|

|

|

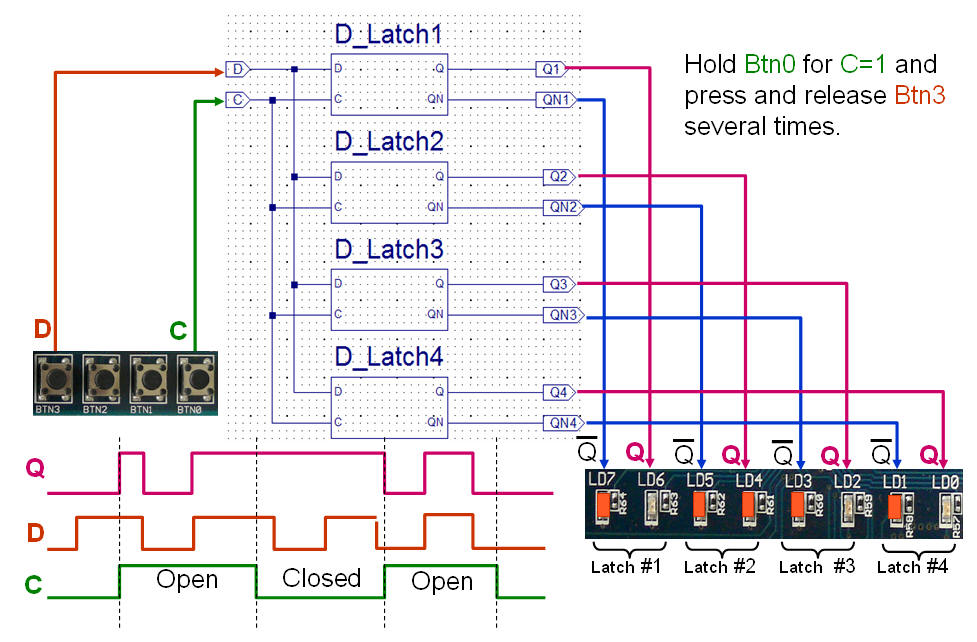

This component can be found in the ISE

schematic libraryPlease note! QN

might give problems in practice, depending on the implementation

in the FPGA

Generally must the Boolean equation

QN = Not Q always be true

|

|

|

|

The Mux-D-Latch not normally found in

textbooks (could it be my own idea?)

However will a multiplexer

normally present a 1- hazard and hence not fitted for

asynchronous feedback loops.

Conclusion - don't use

this in "real-life" even it works perfect in practice.

|

|

|

|

This the most common way to implement a

D-Latch with VHDL.

|

|

What's actually behind a VHDL model???

The synthisise tool (most likely XTS)

use your VHDL code to figure out the functionality of the

circuit you wants.

In the end must this circuit use the

built-in components in the FPGA.

Note how the memory elements can set as

either FF or LATCH with active high or low inputs.

|

A view from

the inside of a Spartan 3E FPGA

|

|

| |

|

|

|

|

|

|

|

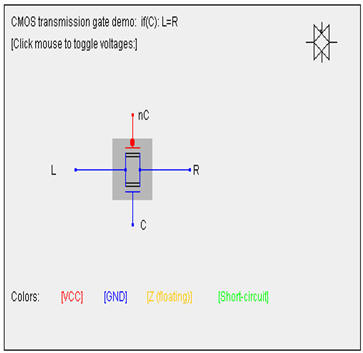

Learn more about the CMOS

D-latch

here

(go to the bottom) |

| |