|

|

|

|

|

|

|

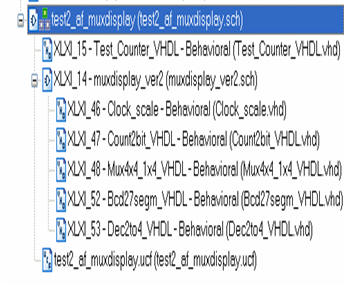

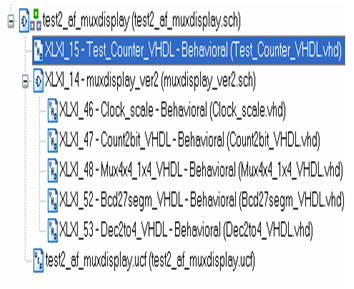

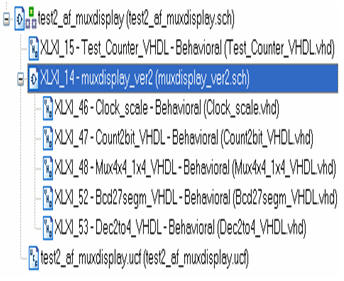

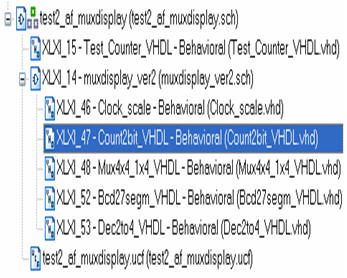

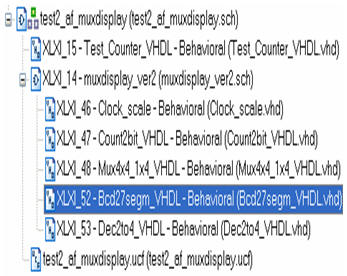

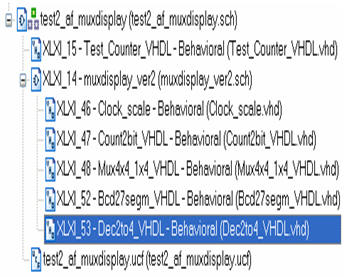

Test Counter

VHDL based

|

|

|

Multiplexed

display version 2

|

|

|

|

|

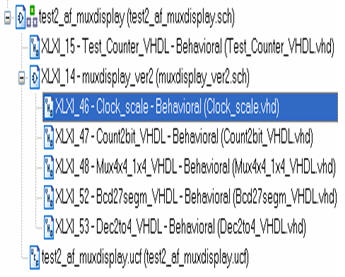

Clock

Downscale Counter - 50 MHz to xxx Hz

|

|

|

|

Note! The least

significant bit# in the counter 0,

hence you must use n = bit# + 1 in

order to calculate the downscaled frequency.

|

|

Counter 2-bit

|

|

|

|

|

Multiplexer

4x4-bit and 4x1-bit

|

|

|

|

|

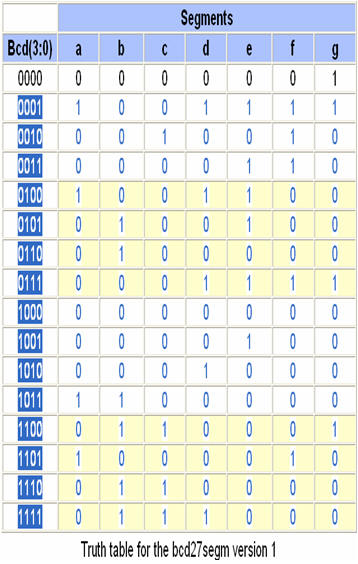

Bcd to

7-segment decoder

|

|

|

|

|

Decoder 2 to 4

(active low outputs)

|

|

|

|

|

|

|

Bcd to 7

segment version 2 - Alternative version

|

|

|

|

|

|

|

| |

|

| |

More solutions

here: Multiplexed

display version 3 - Complete driver in one VHDL module

|