|

| |

|

Last updated:

31-01-09 |

VHDL offers you many

ways to implement a Synchronous State Machine. In most cases

will the resulting hardware be the same as the synthesize tools

recognize your "intensions" even you trying to "fool the tool".

The example concentrate of the

question - Should you use one, two or three processes for your

State Machine.

|

|

|

|

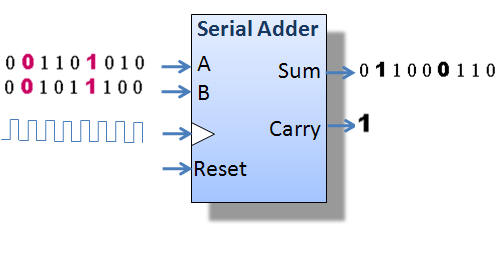

In the old days of computer

science (way back in the 1950ies) was hardware expensive and the

need for speed less.

If you wanted to add two number of say 64-bit length would the

cost of a true parallel adder be unbearable (literally).

On the other hand -If you

where willing to use 64-clock pulses would the hardware cost be

reasonable.

|

|

|

| |

|

| |

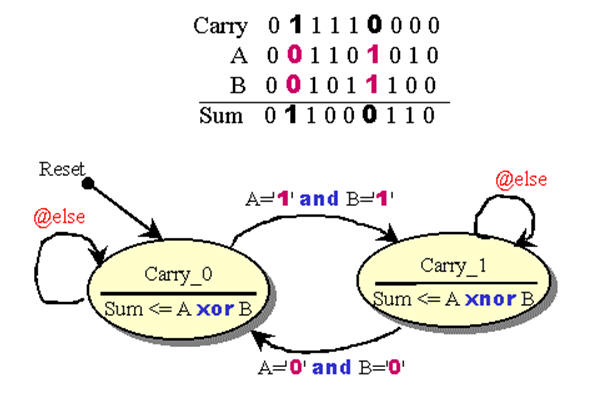

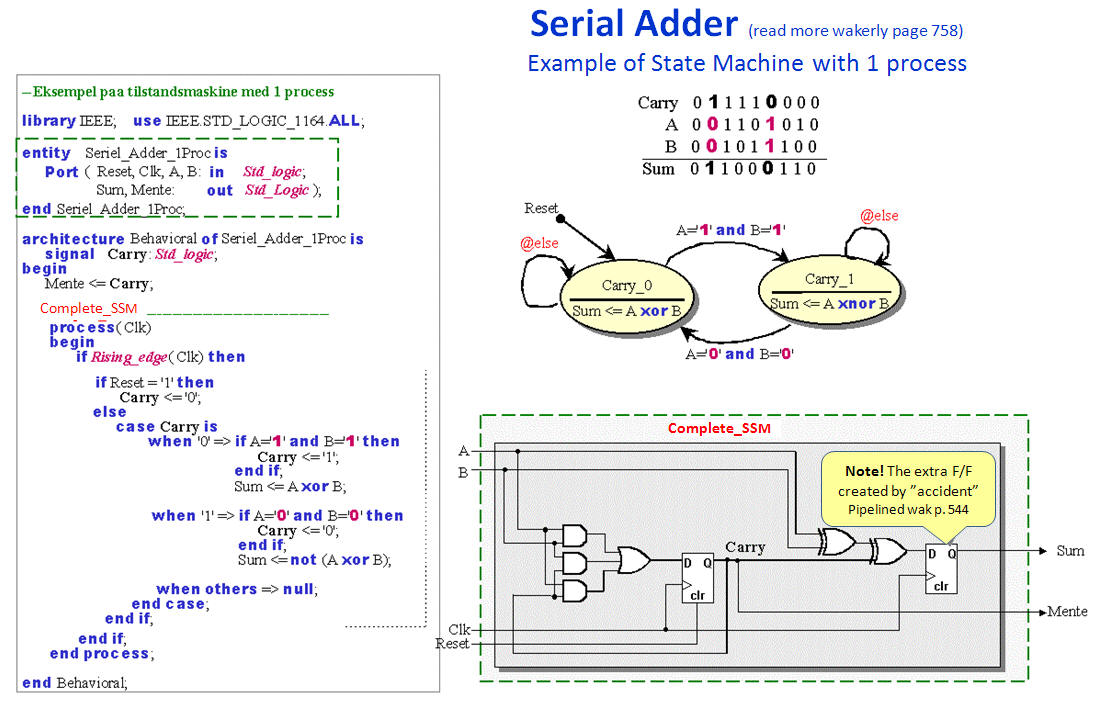

State

Machine with 1 process |

| |

|

| |

The one process

description of a State Machine comes natural - and

could be considered good practice as well.

However must you be

aware that all signals inside a Clock-driven process

will be assigned to a F/F. That's the reason why a

Mealy output like Sum ends like a Pipelined output.

|

| |

|

|

|

|

| |

|

| |

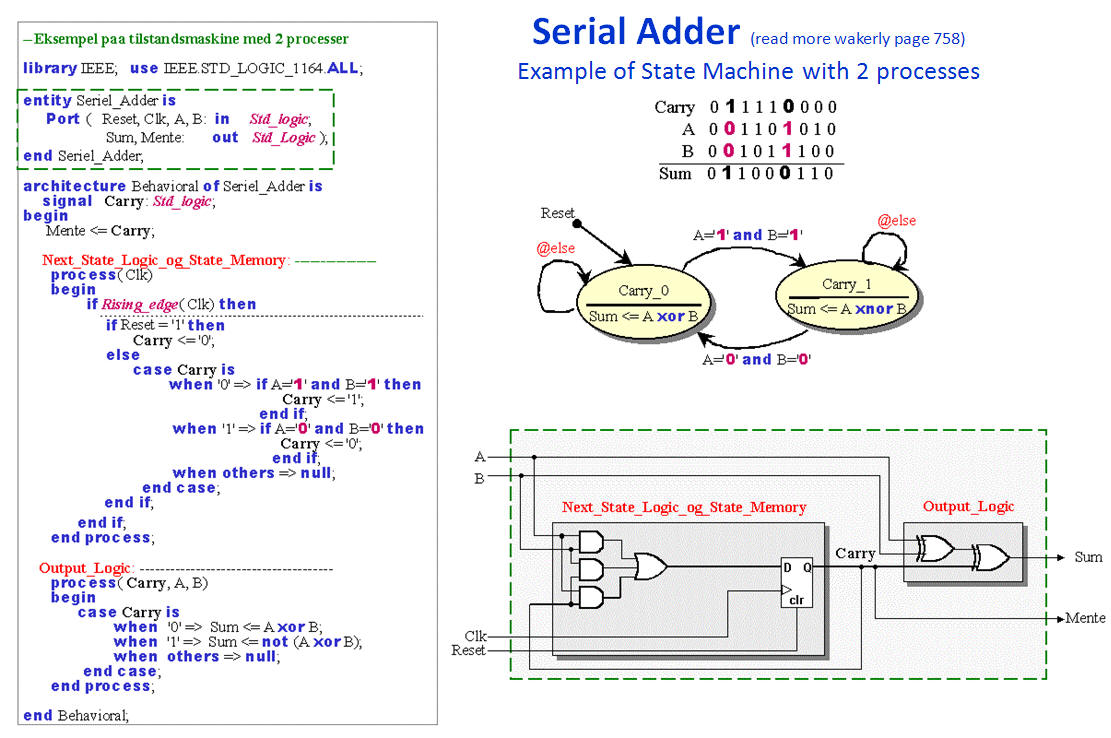

State

Machine with 2 processes |

| |

|

| |

The Two process

description of a State Machine a good choice for a

Mealy type State Machine.

The Output logic process must of course be a

Combinatorial process - Hence must all inputs and

the Current state be in the sensitivity-list.

An alternative could also be "pure" concurrent code.

|

| |

|

|

|

|

| |

|

| |

State

Machine with 3 processes |

| |

|

| |

The Three process

approach could like like a lot of extra effort

without extra gain. How ever must you realize that

as the complexity of the State Machine increases

will the change of errors also increase.

The type errors of the nasty kind - namely errors

which not show up in the synthesize process and only

will show up through simulation and in the real

hardware.By

splitting your design in "pure" combinatorial

process for the Next State logic and a Clock-driven

process for the Next State Logic do you make life

easier for the synthesize tools. The change of

getting this right the first time better.

Please note that

in this example will the 2 Process description

properly be the best choice.

|

| |

|

|

|

|

|

|

|

|

|

|

|

|